# Free-standing silicon shadow masks for transmon qubit fabrication •

Cite as: AIP Advances 10, 065120 (2020); https://doi.org/10.1063/1.5138953 Submitted: 15 November 2019 . Accepted: 23 March 2020 . Published Online: 15 June 2020

I. Tsioutsios , K. Serniak, , S. Diamond, V. V. Sivak, Z. Wang, S. Shankar, L. Frunzio, R. J. Schoelkopf, and M. H. Devoret

### COLLECTIONS

Paper published as part of the special topic on Chemical Physics, Energy, Fluids and Plasmas, Materials Science and Mathematical Physics

This paper was selected as Featured

### ARTICLES YOU MAY BE INTERESTED IN

Machine learning-based approach for automatically tuned feedback-controlled electromigration

AIP Advances 10, 065301 (2020); https://doi.org/10.1063/1.5143051

##

Cite as: AIP Advances 10, 065120 (2020); doi: 10.1063/1.5138953 Submitted: 15 November 2019 • Accepted: 23 March 2020 •

Published Online: 15 June 2020

I. Tsioutsios, (D) K. Serniak, (D) S. Diamond, V. V. Sivak, (D) Z. Wang, (D) S. Shankar, (D) L. Frunzio, (D) R. J. Schoelkopf, (D) and M. H. Devoret

### **AFFILIATIONS**

Department of Applied Physics, Yale University, New Haven, Connecticut 06520, USA

<sup>a)</sup> Authors to whom correspondence should be addressed: ioannis.tsioutsios@yale.edu and michel.devoret@yale.edu

#### **ABSTRACT**

Nanofabrication techniques for superconducting qubits rely on resist-based masks patterned by electron-beam or optical lithography. We have developed an alternative nanofabrication technique based on free-standing silicon shadow masks fabricated from silicon-on-insulator wafers. These silicon shadow masks not only eliminate organic residues associated with resist-based lithography, but also provide a pathway to better understand and control surface-dielectric losses in superconducting qubits by decoupling mask fabrication from substrate preparation. We have successfully fabricated aluminum 3D transmon superconducting qubits with these shadow masks and found coherence quality factors comparable to those fabricated with standard techniques.

© 2020 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/). https://doi.org/10.1063/1.5138953

Progress in superconducting circuits for quantum information technologies relies on the improvement of superconducting qubit lifetimes. One of the main sources of energy loss in these devices comes from the dielectric surfaces surrounding the Josephson junctions and associated superconducting circuitry. In particular, a number of experimental results attribute the majority of dielectric loss to one or several of the device–substrate, substrate–air, and device–air interfaces, rather than the bulk dielectrics. <sup>2–11</sup>

State-of-the-art superconducting qubits are fabricated by patterning an organic resist with e-beam or optical lithography to create a liftoff mask, followed by shadow evaporation of the aluminum layer. <sup>12–18</sup> Inevitably, this approach introduces contamination to various interfaces. <sup>5</sup> This includes organic residues from the resist, contamination from the solvents that are required for the resist development after e-beam exposure, and those required for the lift-off process after metal deposition. Furthermore, degassing of the organic mask during metal deposition can lead to additional contamination.

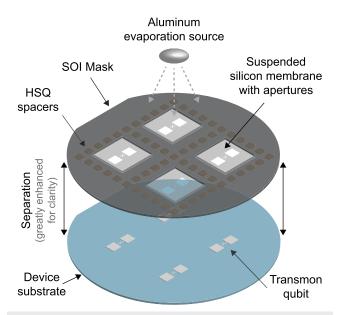

In order to investigate the problems associated with residual contamination and eventually suppress it, we have developed a new nanofabrication technique for superconducting qubits (Fig. 1). Our technique replaces the lift-off of an organic lithography layer with stencil lithography<sup>19</sup> based on

free-standing silicon shadow masks fabricated from silicon-on-insulator (SOI) wafers. Consequently, device substrate preparation becomes completely independent from the mask fabrication. As a result, the nanofabrication-related contamination is significantly reduced, and more importantly, controlled studies of surface dielectric losses as a function of surface preparation are now possible. Moreover, the inorganic mask is compatible with high-temperature processes, such as deposition of refractory metals<sup>20</sup> and substrate annealing, which could be performed *in situ*. The silicon mask is free-standing, and thus can be removed from the target substrate at the end of the process and reused for subsequent depositions. It is also tension-free and therefore has higher mechanical stability relative to other possible stencil methods.

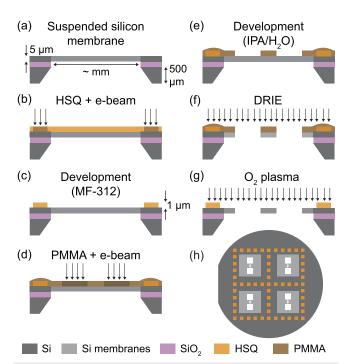

The masks were fabricated from 100 mm SOI wafers, which consist of a 500  $\mu$ m-thick substrate, 200 nm-thick SiO<sub>2</sub> layer, and 5  $\mu$ m-thick silicon top layer. The wafers incorporate a prefabricated array of 60, (2.7 × 8.6) mm<sup>2</sup>, 5  $\mu$ m-thick, suspended silicon membranes, where the silicon substrate and SiO<sub>2</sub> layer were completely etched away.<sup>21</sup> A schematic cross section of a single suspended silicon membrane is illustrated in Fig. 2(a). The fabrication process starts by creating spacers to control the distance between the mask and the device substrate. The wafer was spin coated at 1000 rpm

**FIG. 1.** Concept for nanofabrication of superconducting transmon qubits using free-standing silicon shadow masks (not to scale illustration). A silicon-on-insulator (SOI) wafer incorporates micrometer-thick suspended silicon membranes, which contain apertures with submicron features. The stencil mask is placed on top of another wafer (device substrate). Aluminum is evaporated through it to create transmon structures on the device substrate. The micrometer-size cross-linked HSQ spacers control the distance between the mask and the device substrate. The mask is mechanically separated from the substrate at the end of the aluminum deposition, leaving minimal nanofabrication-related residues. Here, the junction pattern has been caricatured for clarity.

for 2 min with hydrogen silsesquioxane (HSQ-FOx16), which is a negative inorganic e-beam resist [Fig. 2(b)]. It was then patterned in a Vistec electron-beam pattern generator (EBPG-5000+) with a 100 keV electron beam and developed in MF-312 for 5 min, resulting in arrays of  $(200 \times 200) \, \mu \text{m}^2$  and 1  $\mu$ m-thick cross-linked HSQ spacers [Figs. 2(c) and 2(h)]. Transmon patterns were defined by apertures in the silicon membranes, created with another step of e-beam lithography. The wafer was spin coated with the PMMA 950 A7 resist at 1500 rpm, baked for 5 min at 200 °C, exposed with a 100 keV electron beam [Fig. 2(d)], and developed in IPA/H<sub>2</sub>O (3:1) at 6 °C for 2 min [Fig. 2(e)]. The apertures were created in the suspended silicon membranes by the highly anisotropic deep-reactive-ion-etching (DRIE) BOSCH process<sup>22</sup> [Fig. 2(f)]. As a last step, PMMA and other organic residues were removed from the mask with O<sub>2</sub>-plasma cleaning [Fig. 2(g)].

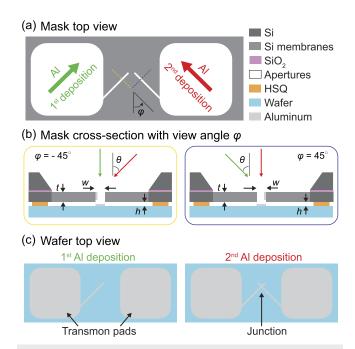

To demonstrate this new nanofabrication method, we focused on a mask design that is suitable for aluminum 3D transmon qubit fabrication. Figure 3 is a simplified schematic describing the metal deposition method. The large rectangular apertures correspond to the capacitor pads and the narrow slits to the leads that will form the Josephson junction of the transmon. The deposition process requires the ability to tilt and rotate the mask-wafer stack with respect to the evaporation source, similarly to that employed in the so-called "Manhattan" process. The first deposition is performed with the stage rotated parallel to the left slit ( $\varphi = -45^{\circ}$ ) and tilted by

**FIG. 2.** [(a)–(g)] Schematic cross section diagrams of the free-standing silicon shadow mask nanofabrication process (further described in the main text). (h) Top view schematic of the mask (not to scale).

angle  $\theta$ , as shown in Figs. 3(a) and 3(b) and determined by considerations below. By selecting the width of the junction slits to be much smaller than the thickness of the suspended silicon membranes, and selecting  $\theta$  accordingly, aluminum is deposited through the left slit and lands on the sidewalls of the right slit [Fig. 3(b)]. To accomplish this, the minimum tilt angle should satisfy  $|\theta| > \arctan(w/t)$ , where w is the width of the slit, and t is the thickness of the silicon membrane. During the first deposition, the two capacitor pads and the first junction lead are formed, as shown in Fig. 3(c). An *in situ* oxidation step is then performed to create the tunnel barrier of the junction. A final (second) aluminum deposition with the stage rotated parallel to the right slit ( $\varphi = 45^{\circ}$ ) and tilted by  $\theta$  creates the second junction lead along with another aluminum layer on both capacitor pads [Fig. 3(c)].

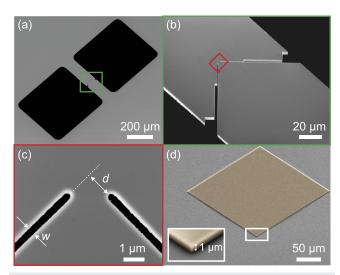

Each fabricated mask contains multiple suspended silicon membranes patterned in that way. In Figs. 4(a)-4(c), scanning electron microscopy (SEM) images of a single silicon membrane of a mask are shown. In every membrane, the capacitor pad apertures have dimensions of  $(530 \times 480) \, \mu \text{m}^2$ . We designed the width of the junction lead slits such that it gradually reduces in order to minimize possible conductive losses from otherwise long and narrow aluminum leads [Fig. 4(b)]. We vary the minimum width of the junction lead slits w, from approximately 200 nm to 400 nm, in order to create transmons with different junction areas from the same mask. Narrower slits would require further optimization of the DRIE process, as well as thinner silicon membranes.<sup>24</sup> In order to increase the mechanical stability of the suspended silicon structure after etching, we opted to end the lead slits well before their crossing

**FIG. 3**. (a) Simplified mask design schematic. The large apertures correspond to the transmon qubit capacitor pads and the narrow slits to the leads of the Josephson tunnel junction. The green and red arrows indicate the orientation of the Al deposition steps. (b) Schematic cross sectional view (not to scale) of the mask at two distinct positions and angles indicated by the yellow and blue lines. Green and red arrows indicate the tilt angle  $\theta$  of the first and second deposition steps, respectively. During the first deposition (green arrows), aluminum will only pass through the left narrow slit (yellow cross section), and it will land on the sidewalls of the other aperture (blue cross section). The reverse process occurs during the second deposition step (red arrows). (c) Top view schematic of the aluminum thin-film structure on the device wafer after each deposition step. The first Al deposition creates two capacitor pads and one thin lead, and the second Al deposition creates a second lead and contributes another layer to the capacitor pads. The Josephson junction is formed where these two leads cross.

point. This imposes an additional condition that the tilt angle satisfies  $|\theta| > \arctan(d/h)$  for the two aluminum junction leads to overlap, where h is the mask–substrate separation. The silicon membrane of  $t=5~\mu \mathrm{m}$  thickness provides the necessary bending rigidity, which further increases the mechanical stability of the suspended structure. Much thinner silicon would require a modified mask design with inplane bridges across the slits. In Fig. 4(d), the SEM image of a (200 × 200)  $\mu \mathrm{m}^2$  and 1  $\mu \mathrm{m}$  thick cross-linked HSQ spacer is shown. Arrays of such spacers across the mask are meant to define h and prevent possible adhesion of the mask on the device substrate due to van der Waals forces.

With the mask shown in Fig. 4, we fabricated arrays of 3D transmons  $^{14}$  on 200  $\mu$ m-thick, 100 mm diameter c-plane sapphire wafers. The sapphire substrates were cleaned in N-methyl-2-pyrrolidone (NMP) at 90 °C for 10 min, sonicated consecutively in NMP, acetone, and isopropyl alcohol (IPA) for 3 min each, and then dried with nitrogen. All metal deposition and oxidation steps were performed in a Plassys UMS300UHV multichamber electron-beam evaporation system without breaking vacuum in-between steps.

**FIG. 4.** [(a)–(c)] Scanning electron microscopy (SEM) images of one of the silicon membranes of our free standing silicon shadow mask. Dark areas correspond to apertures and gray areas to suspended silicon. (d) False color SEM image of a 1  $\mu$ m thick cross-linked HSQ spacer.

After reaching a base pressure less than  $5 \times 10^{-9}$  Torr, we evaporated 21.3 nm aluminum at  $\varphi = -45^{\circ}$  and  $\theta = 20^{\circ}$  at 1 nm/min rate. We then oxidized the aluminum in situ with an O<sub>2</sub>/Ar (3:17) mixture for 15 min at 100 Torr to create the tunnel barrier of the junction. A second evaporation of 31.9 nm aluminum was done at  $\varphi = 45^{\circ}$  and  $\theta = 20^{\circ}$ . A final capping oxidation with an O<sub>2</sub>/Ar (3:17) mixture for 5 min at 50 Torr was then performed. The same mask was employed multiple times on different sapphire wafers. The wafers were diced in  $(8 \times 3)$  mm<sup>2</sup> chips, each containing a single transmon. To do so, we spin coated the wafers with a SC-1827 photoresist layer at 1500 rpm for 2 min and baked it at 90 °C for 9 min. This acts as a protective layer against substrate debris damaging the devices during dicing. The resist was stripped at the end of the dicing process using sequentially NMP, acetone, and IPA. Although the adoption of dicing resist is a convenient practice, it is in conflict here with one of the purposes of our proposed technique, which is to minimize fabrication residues, especially those coming from the organic resist. However, the process of partitioning a wafer into smaller chips is independent of the fabrication of superconducting qubits at the wafer-level, the main focus of our technique. The development of a reliable cleaving technique, which fundamentally does not require protective resist, would be essential for the full elimination of residues on the devices. Nonetheless, acknowledging the above limitation, we tested these devices to determine whether our fabrication technique produces functional transmons.

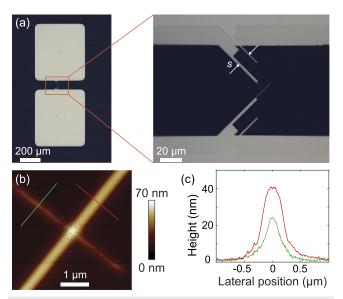

We characterized six of the fabricated aluminum transmon qubits, coming from two separate sapphire wafers, all corresponding to the mask shown in Fig. 4. In what follows, we present extensive results from one representative device and partial results for the other five. In the optical images of Fig. 5(a), one can identify two aluminum layers that correspond to the two distinct evaporation steps. The double-strip pattern is expected for the double evaporation for a wide slit and does not affect the

**FIG. 5.** (a) Optical images of a transmon qubit device fabricated using a free-standing silicon shadow mask. The dark regions correspond to the sapphire substrate and the bright regions to deposited aluminum. (b) Atomic force microscopy (AFM) image of its Josephson junction formed at the crossing point of the two aluminum leads. (c) Height profile for each of the two aluminum leads at the cross sections indicated by green and red color lines in (b).

functionality of the devices. Nonetheless, the distance s between the two strips provides an estimate for the effective mask-substrate separation of  $h_{\rm eff} = s/\tan\theta = 37 \ \mu \rm m$ . This value is much larger than the thickness of the HSQ spacers (1  $\mu$ m). We attribute this to built-in residual compressive strain in the silicon device layer of the SOI wafer,<sup>25</sup> which leads to buckling of the silicon membranes upon their release from the Si/SiO<sub>2</sub> substrate. Nevertheless, a notable characteristic of our mask design is that the junction overlap area is approximately independent of the mask-substrate separation, as it is only defined by the width of the two slits. This contrasts with the results of the Dolan bridge technique, 12 in which the junction area depends on both the mask-substrate separation and the width of the slits. We further characterized the device by taking atomic force microscopy (AFM) images of its junction [Fig. 5(b)]. The asymmetry of the widths of the junction leads may be related to misalignment from the intended rotation angle  $\varphi$ , fabrication variances of the mask aperture widths, or more possibly due to different deposition thicknesses for each lead. A characteristic of this technique is that the deposited metallic thin films tend to have larger dimensions than the mask aperture sizes and softer edge profile [Fig. 5(c)], compared to traditional lift-off-based fabrication technologies. This blurring effect can have two distinct origins: the diffusion of the deposited material on the clean, resist-free surface of the substrate, and the geometry of the metal deposition process, which depends on the aluminum source size D, the source–mask separation H, and the mask-substrate separation  $h^{19,26}$  The metal deposition setup that was used has a source size of D = 5 mm and a source-mask separation of H = 0.6 m. For an effective mask-substrate separation of  $h_{\rm eff}$  = 37  $\mu$ m, the enlargement of the feature sizes due to geometrical factors can be estimated to be  $w_e = Dh/H = 0.31 \mu m$ .

Knowing that the mask aperture widths that were used for this specific transmon were approximately 200 nm, this second effect partly explains the aluminum leads profile of the device [Fig. 5(c)]. However, it cannot be the only feature enlargement effect, since the profile of the sidewalls is less steep than one would expect if the enlargement effect was only due to geometric factors. Therefore, we believe that the resulting soft and elongated cross section profile of the aluminum junction leads [Fig. 5(c)] is a convolution of both diffusion and geometric effects. As blurring can be a limiting factor for smaller junction sizes, further investigation and modeling of the metal deposition dynamics are required. We further characterized the tunnel junction properties of the device, by measuring the normal-state resistance  $R_n = 6.9 \text{ k}\Omega$  of its tunnel junction, employing two-probe DC measurements, and estimating the critical current to be  $I_c = 41$ nA with the Ambegaokar–Baratoff formula  $I_c = (\pi \Delta)/(2eR_n)$ , where  $\Delta = 180 \,\mu\text{eV}$  is the aluminum superconducting gap. This value corresponds to a critical current density of  $J_c = 33 \text{ A/cm}^2$ , assuming a junction area of  $A_i = 0.12 \ \mu \text{m}^2$ , as extracted from the full-widthhalf-maximum of the junction lead profiles [Fig. 5(c)]. The average critical current density that we measured for all the devices fabricated with the same mask on the same sapphire substrate is  $\bar{J}_c$  =  $42 \pm 10 \text{ A/cm}^2$ . This value is similar to those measured for usual aluminum tunnel junctions that we have fabricated with standard techniques and similar oxidation parameters.

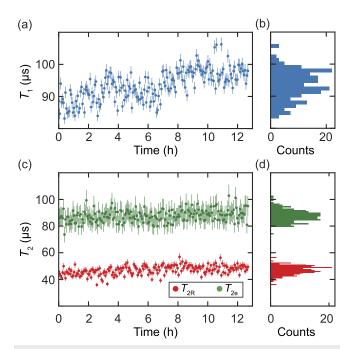

The coherence properties of the transmon qubit, which is shown in Fig. 5, were measured in a dilution refrigerator with a base temperature of approximately 20 mK, adopting a standard circuit quantum electrodynamics (cQED) architecture in the dispersive readout regime.<sup>27</sup> The chip was mounted in an aluminum 3D rectangular-waveguide readout cavity<sup>14</sup> with fundamental mode at frequency  $\omega_r/2\pi = 9.1$  GHz (supplementary material). The measurements were performed in reflection and the input/output signals were coupled to the cavity through a single port with coupling rate set at  $\kappa/2\pi = 2.5$  MHz. The reflected signal from the readout cavity was amplified by a near quantum limited Josephson arraymode parametric amplifier (JAMPA).<sup>28</sup> The transmon had groundto-first-excited-state transition frequency  $\omega_{\rm ge}/2\pi = 6.01$  GHz, anharmonicity  $\alpha/2\pi = \omega_{ge} - \omega_{ef} = 0.23$  GHz, and cross-Kerr to the readout cavity mode  $\chi_{qr}$  = 1.2 MHz. We characterized its coherence properties by performing interleaved repeated measurements of its  $T_1$ energy relaxation time, T<sub>2R</sub> Ramsey, and T<sub>2e</sub> Hahn echo dephasing times for approximately 13 h [Fig. 6]. The length of each measurement was 64 s, 101 s, and 65 s, respectively. We found that the coherence values fluctuate in time with mean values of  $\overline{T}_1 \cong 95 \ \mu s$ ,  $\overline{T}_{2R} \cong 50 \ \mu s$ ,  $\overline{T}_{2e} \cong 85 \ \mu s$ , and standard deviations of  $\sigma_{T_1} \cong 5 \ \mu s$ ,  $\sigma_{T_{2R}} \cong 3 \ \mu s$ , and  $\sigma_{T_{2e}} \cong 5 \ \mu s$ . The measured  $\overline{T}_1$  corresponds to a quality factor of  $\overline{Q}_{ge} \cong 3.5 \times 10^6$ , which is comparable to the state-of-the-art aluminum transmon qubits.<sup>29</sup> Nevertheless, further experimental studies are required to determine whether the energy relaxation properties of this device are limited by surface dielectric losses, nonequilibrium quasiparticle excitations, 29,30 or other loss mechanisms. The fluctuations of  $T_1$  and  $T_2$  as a function of time are similar to what we and other groups 14,29,31 have observed with the same aluminum transmons but fabricated with standard techniques, and can be explained by uncontrolled sources of noise or fluctuating loss channels in the device. The low  $T_{2R}$  Ramsey and  $T_{2e}$ Hahn echo dephasing times, compared to the  $T_2 = 2T_1$  limit, can

**FIG. 6**. [(a) and (c)] Fluctuations of the coherence of the transmon qubit, which is shown in Fig. 5, as a function of time. Interleaved measurements of  $T_1,\,T_{2R}$  Ramsey, and  $T_{2e}$  Hahn echo times were performed for approximately 13 h, with sampling times of 64 s, 101 s, and 65 s, respectively. The resulting mean measured values were  $\overline{T}_1\cong95~\mu s,\,\overline{T}_{2R}\cong50~\mu s,$  and  $\overline{T}_{2e}\cong85~\mu s.$  [(b) and (d)] Corresponding histograms for the measurements with standard deviations of  $\sigma_{T_1}\cong5~\mu s,\,\sigma_{T_{2R}}\cong3~\mu s,$  and  $\sigma_{T_{2e}}\cong5~\mu s.$

be attributed to the residual thermal photon population in the 3D aluminum readout cavity modes. <sup>32</sup> The reproducibility of the fabrication technique was further assessed with coherence measurements of five more devices, fabricated with the same mask on two separate sapphire wafers. All measurements yielded transmons with energy relaxation times of more than 16  $\mu$ s. A table with the full properties of all measured transmons that have been fabricated with the presented technique is given in the supplementary material.

Single tunnel junctions have been previously fabricated with free-standing shadow masks based on silicon nitride (Si<sub>3</sub>N<sub>4</sub>) membranes.<sup>33,34</sup> However, in these efforts, the auxiliary probe-electrodes were fabricated in a separate step in advance. An advantage of freestanding membranes based on silicon, compared to Si<sub>3</sub>Ni<sub>4</sub>, is that they are nominally free from residual in-plane tensile stress. As a result, silicon masks are mechanically robust enough to implement complex asymmetric aperture designs, allowing for better control of the Josephson junction area independent of the mask-substrate separation. Additionally, large and small features can coexist on the same membrane. This provided us the means to fabricate tunnel junctions and the necessary auxiliary circuitry of a superconducting qubit device, such as the large capacitor pads of a 3D transmon qubit, using a single free-standing mask, reducing fabrication residues on the entire qubit device. Furthermore, our technique eliminates the need to align the tunnel junction with respect to the auxiliary circuitry. Inorganic shadow masks based on the Ge/Nb bilayer have also been used for the fabrication of aluminum tunnel junctions by Welander et~al. In their work, Ge/Nb thin films are deposited and processed directly on the device substrate, which could potentially introduce additional contamination relative to free-standing inorganic masks.

In conclusion, we have developed a novel nanofabrication technique for superconducting qubits that is based on inorganic freestanding silicon shadow masks, fabricated from SOI wafers. We fabricated aluminum 3D transmon qubits with these masks and performed preliminary observations of their coherence properties. Our work addresses the residual contamination drawbacks inherent to e-beam and optical lithography techniques, providing a solid experimental platform to better understand, control, and potentially minimize surface-dielectric losses in planar superconducting circuits. This technique accomplishes full decoupling of the mask fabrication from device substrate preparation and thus minimizes crosscontamination between the mask and the device substrate. Systematic investigations of the effect of substrate treatment on surface dielectric losses without the restrictions imposed by organic resist processes are made possible. A key advantage of inorganic masks is their ability to sustain high metal deposition temperatures. To this end, free-standing silicon shadow masks hold promise as a suitable technique to fabricate high-quality superconducting qubits based on refractory materials with a larger superconducting gap, such as niobium or tantalum.<sup>20</sup> In addition, high temperature substrate annealing8 can now be achieved in situ, under high vacuum, just before metal deposition, to further improve the surface properties of the device wafer. Finally, this technique is fully compatible with the fabrication of planar superconducting resonators, bringing to these necessary auxiliaries of tunnel junctions all of the aforementioned advantages.

See the <u>supplementary material</u> for more information regarding the cryogenic microwave measurement setup and the full properties of all measured transmon qubits.

We acknowledge insightful discussions with Michael Rooks, Michael Power, Shantanu Mundhada, Chan U Lei, and Andrew Saydjari. The use of the facilities was supported by YINQE and the Yale SEAS cleanroom. This research was supported by the Army Research Office (ARO) under Grant Nos. W911NF-18-1-0212 and W911NF-18-1-0020 and by the Multidisciplinary University Research Initiatives-Office of Naval Research (MURI-ONR) under Grant No. N00014-16-1-2270.

### **REFERENCES**

<sup>1</sup>M. H. Devoret and R. J. Schoelkopf, "Superconducting circuits for quantum information: An outlook," Science **339**(6124), 1169–1174 (2013).

<sup>2</sup>K. Geerlings, S. Shankar, E. Edwards, L. Frunzio, R. J. Schoelkopf, and M. H. Devoret, "Improving the quality factor of microwave compact resonators by optimizing their geometrical parameters," Appl. Phys. Lett. **100**(19), 192601 (2012).

<sup>3</sup>W. D. Oliver and P. B. Welander, "Materials in superconducting quantum bits," MRS Bull. 38(10), 816–825 (2013).

<sup>4</sup>J. M. Martinis and A. Megrant, "UCSB final report for the CSQ program: Review of decoherence and materials physics for superconducting qubits," arXiv:1410.5793v1 (2014).

<sup>5</sup>C. M. Quintana, A. Megrant, Z. Chen, A. Dunsworth, B. Chiaro, R. Barends, B. Campbell, Yu Chen, I. C. Hoi, E. Jeffrey, J. Kelly, J. Y. Mutus, P. J. J. O'Malley,

- C. Neill, P. Roushan, D. Sank, A. Vainsencher, J. Wenner, T. C. White, A. N. Cleland, and J. M. Martinis, "Characterization and reduction of microfabrication-induced decoherence in superconducting quantum circuits," Appl. Phys. Lett. **105**(6), 062601(2014).

- <sup>6</sup>C. Wang, C. Axline, Y. Y. Gao, T. Brecht, Y. Chu, L. Frunzio, M. H. Devoret, and R. J. Schoelkopf, "Surface participation and dielectric loss in superconducting qubits," Appl. Phys. Lett. **107**(16), 162601 (2015).

- <sup>7</sup>O. Dial, D. T. McClure, S. Poletto, G. A. Keefe, M. B. Rothwell, J. M. Gambetta, D. W. Abraham, J. M. Chow, and M. Steffen, "Bulk and surface loss in superconducting transmon qubits," Supercond. Sci. Technol. **29**(4), 044001 (2016).

- <sup>8</sup> A. Kamal, J. L. Yoder, F. Yan, T. J. Gudmundsen, D. Hover, A. P. Sears, P. Welander, T. P. Orlando, S. Gustavsson, and W. D. Oliver, "Improved superconducting qubit coherence with high-temperature substrate annealing," arXiv:1606.09262v1 (2016).

- <sup>9</sup>J. M. Gambetta, C. E. Murray, Y.-K.-K. Fung, D. T. Mcclure, O. Dial, W. Shanks, J. W. Sleight, and M. Steffen, "Investigating surface loss effects in superconducting transmon qubits," IEEE Trans. Appl. Supercond. **27**(1), 1–5 (2017).

- <sup>10</sup>G. Calusine, A. Melville, W. Woods, R. Das, C. Stull, V. Bolkhovsky, D. Braje, D. Hover, D. K. Kim, X. Miloshi, D. Rosenberg, A. Sevi, J. L. Yoder, E. Dauler, and W. D. Oliver, "Analysis and mitigation of interface losses in trenched superconducting coplanar waveguide resonators," Appl. Phys. Lett. 112(6), 062601 (2018).

- <sup>11</sup>W. Woods, G. Calusine, A. Melville, A. Sevi, E. Golden, D. K. Kim, D. Rosenberg, J. L. Yoder, and W. D. Oliver, "Determining interface dielectric losses in superconducting coplanar-waveguide resonators," Phys. Rev. Appl. 12(1), 014012 (2019).

- <sup>12</sup>G. J. Dolan, "Offset masks for lift-off photoprocessing," Appl. Phys. Lett. 31(5), 337–339 (1977).

- <sup>13</sup>F. Lecocq, I. M. Pop, Z. Peng, I. Matei, T. Crozes, T. Fournier, C. Naud, W. Guichard, and O. Buisson, "Junction fabrication by shadow evaporation without a suspended bridge," Nanotechnology 22(31), 315302 (2011).

- <sup>14</sup>H. Paik, D. I. Schuster, L. S. Bishop, G. Kirchmair, G. Catelani, A. P. Sears, B. R. Johnson, M. J. Reagor, L. Frunzio, L. I. Glazman, S. M. Girvin, M. H. Devoret, and R. J. Schoelkopf, "Observation of high coherence in Josephson junction qubits measured in a three-dimensional circuit QED architecture," Phys. Rev. Lett. 107(24), 240501 (2011).

- <sup>15</sup>R. Barends, J. Kelly, A. Megrant, D. Sank, E. Jeffrey, Y. Chen, Y. Yin, B. Chiaro, J. Mutus, C. Neill, P. O'Malley, P. Roushan, J. Wenner, T. C. White, A. N. Cleland, and J. M. Martinis, "Coherent Josephson qubit suitable for scalable quantum integrated circuits," Phys. Rev. Lett. 111(8), 080502 (2013).

- <sup>16</sup>I. M. Pop, K. Geerlings, G. Catelani, R. J. Schoelkopf, L. I. Glazman, and M. H. Devoret, "Coherent suppression of electromagnetic dissipation due to superconducting quasiparticles," Nature **508**(7496), 369–372 (2014).

- <sup>17</sup>F. Yan, S. Gustavsson, A. Kamal, J. Birenbaum, A. P. Sears, D. Hover, D. Rosenberg, G. Samach, T. J. Gudmundsen, J. L. Yoder, T. P. Orlando, J. Clarke, A. J. Kerman, and W. D. Oliver, "The flux qubit revisited to enhance coherence and reproducibility," Nat. Commun. 7, 12964 (2016).

- <sup>18</sup>N. Foroozani, C. Hobbs, C. C. Hung, S. Olson, D. Ashworth, E. Holland, M. Malloy, P. Kearney, B. O'Brien, B. Bunday, D. DiPaola, W. Advocate, T. Murray, P. Hansen, S. Novak, S. Bennett, M. Rodgers, B. Baker-O'Neal, B. Sapp, E. Barth, J. Hedrick, R. Goldblatt, S. S. P. Rao, and K. D. Osborn, "Development of transmon qubits solely from optical lithography on 300 mm wafers," Quantum Sci. Technol. 4(2), 025012 (2019).

- <sup>19</sup>O. Vazquez-Mena, L. Gross, S. Xie, L. G. Villanueva, and J. Brugger, "Resistless nanofabrication by stencil lithography: A review," <u>Microelectron. Eng.</u> 132, 236–254 (2015).

- <sup>20</sup> A. P. M. Place, L. V. H. Rodgers, P. Mundada, B. M. Smitham, M. Fitz-patrick, Z. Leng, A. Premkumar, J. Bryon, S. Sussman, G. Cheng, T. Madhavan, H. K. Babla, B. Jaeck, A. Gyenis, N. Yao, R. J. Cava, N. P. de Leon, and A. A. Houck, "New material platform for superconducting transmon qubits with coherence times exceeding 0.3 milliseconds," arXiv:2003.00024v1 (2020).

- <sup>21</sup>See www.norcada.com for Norcada, Inc.

- <sup>22</sup>F. Laermer and A. Schilp, "Method of anisotropically etching silicon," U.S. patent US5501893A (26 March 1996).

- <sup>23</sup>S. Gladchenko, D. Olaya, E. Dupont-Ferrier, B. Douçot, L. B. Ioffe, and M. E. Gershenson, "Superconducting nanocircuits for topologically protected qubits," Nat. Phys. 5(1), 48–53 (2009).

- <sup>24</sup>J. Yeom, Y. Wu, J. C. Selby, and M. A. Shannon, "Maximum achievable aspect ratio in deep reactive ion etching of silicon due to aspect ratio dependent transport and the microloading effect," J. Vac. Sci. Technol., B **23**(6), 2319 (2006).

- <sup>25</sup>T. Iida, T. Itoh, D. Noguchi, and Y. Takano, "Residual lattice strain in thin silicon-on-insulator bonded wafers: Thermal behavior and formation mechanisms," J. Appl. Phys. **87**(2), 675–681 (2000).

- <sup>26</sup>C. W. Park, J. Brugger, L. Guillermo Villanueva, V. Savu, K. Sidler, and O. Vazquez-Mena, "Reliable and improved nanoscale stencil lithography by membrane stabilization, blurring, and clogging corrections," IEEE Trans. Nanotechnol. **10**(2), 352–357 (2010).

- <sup>27</sup> A. Blais, R. S. Huang, A. Wallraff, S. M. Girvin, and R. J. Schoelkopf, "Cavity quantum electrodynamics for superconducting electrical circuits: An architecture for quantum computation," Phys. Rev. A 69(6), 062320 (2004).

- <sup>28</sup>V. V. Sivak, S. Shankar, G. Liu, J. Aumentado, and M. H. Devoret, "Josephson array-mode parametric amplifier," Phys. Rev. Appl. **13**(2), 024014 (2020).

- <sup>29</sup>K. Serniak, S. Diamond, M. Hays, V. Fatemi, S. Shankar, L. Frunzio, R. J. Schoelkopf, and M. H. Devoret, "Direct dispersive monitoring of charge parity in offset-charge-sensitive transmons," Phys. Rev. Appl. **12**(1), 014052 (2019).

- <sup>30</sup> K. Serniak, M. Hays, G. De Lange, S. Diamond, S. Shankar, L. D. Burkhart, L. Frunzio, M. Houzet, and M. H. Devoret, "Hot nonequilibrium quasiparticles in transmon qubits," Phys. Rev. Lett. **121**(15), 157701 (2018).

- <sup>31</sup>P. V. Klimov, J. Kelly, Z. Chen, M. Neeley, A. Megrant, B. Burkett, R. Barends, K. Arya, B. Chiaro, Yu Chen, A. Dunsworth, A. Fowler, B. Foxen, C. Gidney, M. Giustina, R. Graff, T. Huang, E. Jeffrey, E. Lucero, J. Y. Mutus, O. Naaman, C. Neill, C. Quintana, P. Roushan, D. Sank, A. Vainsencher, J. Wenner, T. C. White, S. Boixo, R. Babbush, V. N. Smelyanskiy, H. Neven, and J. M. Martinis, "Fluctuations of energy-relaxation times in superconducting qubits," Phys. Rev. Lett. 121(9), 090502 (2018).

- <sup>32</sup>Z. Wang, S. Shankar, Z. K. Minev, P. Campagne-Ibarcq, A. Narla, and M. H. Devoret, "Cavity attenuators for superconducting qubits," Phys. Rev. Appl. 11(1), 014031 (2019).

- <sup>33</sup>Y. Ootuka, K. Ono, H. Shimada, and S.-I. Kobayashi, "A new fabrication method of ultra small tunnel junctions," Physica B **227**(1-4), 307–309 (1996).

- <sup>34</sup>V. Savu, J. Kivioja, J. Ahopelto, and J. Brugger, "Quick and clean: Stencil lithography for wafer-scale fabrication of superconducting tunnel junctions," IEEE Trans. Appl. Supercond. 19(3), 242–244 (2009).

- $^{\bf 35}$ P. B. Welander, V. Bolkhovsky, T. J. Weir, M. A. Gouker, and W. D. Oliver, "Shadow evaporation of epitaxial Al/Al<sub>2</sub>O<sub>3</sub>/Al tunnel junctions on sapphire utilizing an inorganic bilayer mask," arXiv:1203.6007v1 (2012).